# 85W Power Transistor Gan HEMT on SiC

# **Description**

The CHK9013-99F is a 85W Gallium Nitride High Electron Mobility Transistor.

This product offers a general purpose and broadband solution for a variety of RF power applications such as radar and telecommunication.

The circuit is manufactured on a 0.25µm gate length GaN HEMT technology on SiC substrate.

It is proposed in a bare die form and requires an external matching circuitry.

#### **Main Features**

- Wide band capability up to 8GHz

- Pulsed and CW operating modes

- GaN technology: High Pout & High PAE

- DC bias: V<sub>D</sub> up to 30V■ Chip size: 0.9x4.27x0.1mm

- RoHS N°2011/65 ■ REACh N°1907/2006

#### **Main Electrical Characteristics**

Tref= +25°C, pulsed mode, Freq=6GHz,  $V_{DS}$ =30V,  $I_{D_{-}Q}$ =1.1A

| Symbol               | Parameter                  | Min | Тур | Max | Unit |

|----------------------|----------------------------|-----|-----|-----|------|

| Gss                  | Small Signal Gain          |     | 18  |     | dB   |

| P <sub>SAT</sub>     | Saturated Output Power     |     | 88  |     | W    |

| PAE                  | Max Power Added Efficiency |     | 65  |     | %    |

| G <sub>PAE_MAX</sub> | Associated Gain at Max PAE |     | 14  |     | dB   |

These values are deduced from elementary power cell performances.

Ref.: DSCHK90130301 - 27 Oct 20

Specifications subject to change without notice

# **Recommended Operating Ratings**

Tref = +25°C

| Symbol               | Parameter                    | Min | Тур  | Max     | Un<br>it | Conditions                               |

|----------------------|------------------------------|-----|------|---------|----------|------------------------------------------|

| $V_{DS}$             | Drain to Source Voltage      |     |      | 30      | V        |                                          |

| V <sub>GS</sub>      | Gate to Source Voltage       |     | -3.3 |         | V        | $V_{DS}$ =30V, $I_{D_Q}$ =1.1A           |

| V <sub>DG_peak</sub> | Drain-Gate Voltage           |     | 80   |         | V        | DC+RF                                    |

| VGS_peak             | Gate-Source Voltage          | -20 |      |         | V        | DC+RF                                    |

| $I_{D_Q}$            | Quiescent Drain Current      |     | 1.1  | 2.5 (1) | Α        | V <sub>DS</sub> =30V                     |

| I <sub>D_MAX</sub>   | Drain Current                |     |      | 5.7 (1) | Α        | V <sub>DS</sub> =30V,<br>compressed mode |

| I <sub>G_MAX</sub>   | Gate Current in forward mode |     | 0    | 90      | mA       | DC or Compressed mode                    |

| T <sub>j_MAX</sub>   | Junction temperature         |     |      | 200     | °C       | (1)                                      |

<sup>(1)</sup> Power dissipation must be considered.

### **DC Characteristics**

Tref= +25°C

| Symbol              | Parameter                        | Min  | Тур  | Max  | Unit | Conditions                                                 |

|---------------------|----------------------------------|------|------|------|------|------------------------------------------------------------|

| V <sub>P</sub>      | Pinch-Off Voltage                | -4   | -3.4 | -2.8 | V    | V <sub>D</sub> =10V,I <sub>D</sub> = I <sub>DSS</sub> /100 |

| I <sub>D_SAT</sub>  | Saturated Drain Current          |      | 20   |      | Α    | $^{(1)}$ , $V_D=10V$ , $V_G=1V$                            |

| I <sub>G_leak</sub> | Gate Leakage Current             | -4.4 |      |      | mA   | $V_D=50V, V_G=-7V$                                         |

| $V_{BDG}$           | Drain-Gate Break-down<br>Voltage |      | 120  |      | V    | V <sub>G</sub> =-7V, I <sub>D</sub> =20mA                  |

<sup>(1)</sup> For information, limited by I<sub>D MAX</sub>, see on ROR & AMR.

#### **RF Characteristics**

Tref= +25°C, pulsed mode, Freq=6GHz, V<sub>DS</sub>=30V, I<sub>D Q</sub>=1.1A

| Symbol               | Parameter                  | Min | Тур | Max | Unit | Conditions |

|----------------------|----------------------------|-----|-----|-----|------|------------|

| Gss                  | Small Signal Gain          |     | 18  |     | dB   |            |

| P <sub>SAT</sub>     | Saturated Output Power     |     | 88  |     | W    |            |

| PAE                  | Max Power Added Efficiency |     | 65  |     | %    |            |

| G <sub>PAE_MAX</sub> | Associated Gain at Max PAE |     | 14  |     | dB   |            |

These values are deduced from elementary power cell performances.

#### **Absolute Maximum Ratings**

Tref =  $+25^{\circ}C^{(1)(2)(3)}$

| Symbol               | Parameter                    | Rating      | Unit | Note     |

|----------------------|------------------------------|-------------|------|----------|

| V <sub>DS</sub>      | Drain-Source Biasing Voltage | 55          | V    |          |

| V <sub>G</sub> S     | Gate-Source Biasing Voltage  | -15, +2     | V    | (4), (5) |

| V <sub>DG_peak</sub> | Drain-Gate Voltage (DC+RF)   | 120         | V    |          |

| VGS_peak             | Gate-Source Voltage (DC+RF)  | -25         | V    |          |

| I <sub>G_MAX</sub>   | Maximum Gate Current         | 175         | mA   |          |

| I <sub>G_MIN</sub>   | Minimum Gate Current         | -11         | mA   |          |

| I <sub>D_MAX</sub>   | Maximum Drain Current        | See note    |      | (4)      |

| P <sub>IN</sub>      | Maximum Input Power          | See note    |      | (5)      |

| Tj                   | Maximum Junction Temperature | 230         | °C   |          |

| T <sub>STG</sub>     | Storage Temperature          | -55 to +150 | °C   |          |

| T <sub>Case</sub>    | Case Operating Temperature   | See note    | °C   | (4)      |

<sup>(1)</sup> Operation of this device above anyone of these parameters may cause permanent damage.

# Biasing procedure

- 1. Bias power bar gate voltage at Vg close to  $V_{pinch-off}$  (Typically:  $V_{GS} \approx -5V$ )

- 2. Apply  $V_{DS}$  bias voltage (Typically:  $V_{DS} = 30V$ )

- 3. Increase V<sub>GS</sub> up to guiescent bias drain current I<sub>D Q</sub>

The quiescent current steady state must be carefully controlled as it is influenced by the operating mode, the temperature and the overall thermal resistance.

A drain current control is recommended on the biasing network.

<sup>(2)</sup> Duration < 1s.

<sup>&</sup>lt;sup>(3)</sup> The given values must not be exceeded at the same time even momentarily for any parameter, since each parameter is independent from each other, otherwise deterioration or destruction of the device may take place.

<sup>(4)</sup> Max junction temperature must be considered.

<sup>&</sup>lt;sup>(5)</sup> Linked to and limited by Ig\_max & Ig\_min values. Maximum input power depends on frequency and should not exceed 2dB above PAE\_max.

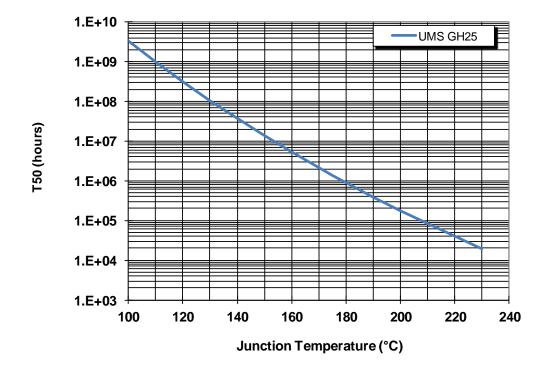

#### **Device thermal information**

The thermal performances of the device are based on UMS rules to evaluate the junction temperature (Tj). This temperature is defined as the peak temperature in the channel area.

This same procedure is the basis for junction temperature evaluation of the samples used to derive the Median lifetime and activation energy for the particular technology on which the CHK9013-99F is fabricated (GaN Power PHEMT 0.25µm).

The temperature Tb is defined as the chip back side temperature

The thermal resistance (Rth) is given for the full power bar, in "equivalent" CW operating mode and in two different configurations as given in the table. The device assembly must be adapted to the operating mode. Thermal analysis is recommended. More information is available on request.

| Parameters                    | Symbol | Conditions                          | Value | Unit |

|-------------------------------|--------|-------------------------------------|-------|------|

| Typical Thermal<br>Resistance | Rth    | Bare die characteristic<br>Tb=125°C | 0.9   | °C/W |

| Junction Temperature          | Tj     | Pdiss=83W<br>CW                     | 200   | °C   |

The back side temperature (Tb) is considered uniform on all the surface

| Typical Thermal<br>Resistance | Rth | Bare die on carrier characteristic Tc=85°C | 2.1 | °C/W |

|-------------------------------|-----|--------------------------------------------|-----|------|

| Junction Temperature          | Tj  | Pdiss=55W<br>CW                            | 200 | °C   |

The reference temperature (Tc) is defined on the carrier back side. The power bar is mounted on carrier plate (20µm Au/Sn soldering + 1.4mm Cu/Mo/Cu).

#### **Median Life Time versus Junction Temperature**

...iii ums

Ref.: DSCHK90130301 - 27 Oct 20

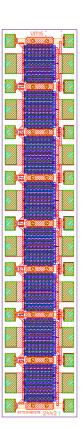

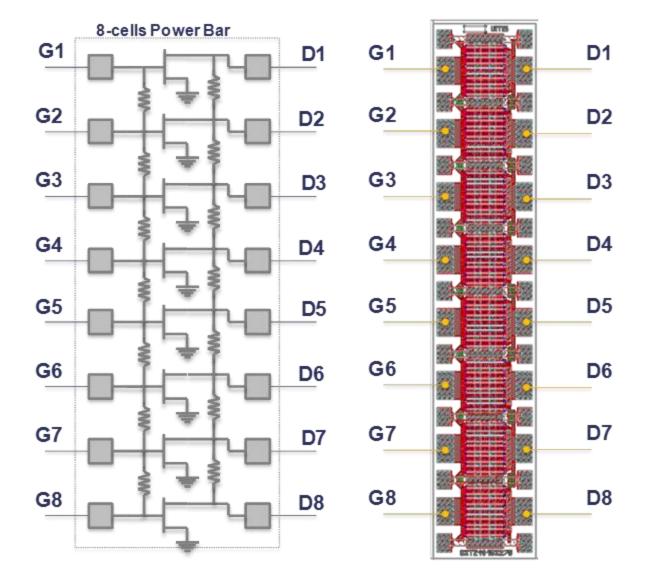

## **Power Bar Description**

The device is composed of 8x11W elementary cells. These cells are connected together with a specific network providing a good trade-off between performance and stability (resistance between gates and drains as described on the schematic). The reference planes are on the center of the bonding pads.

A multiport non-linear model is available on request.

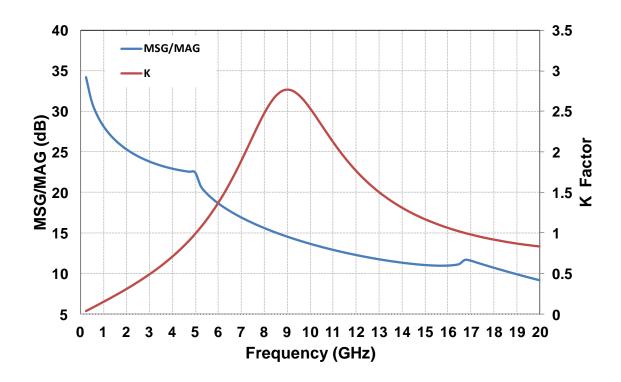

# **Elementary Cell Maximum Gain & Stability Characteristics**

Tref = +25°C,  $V_{DS} = +30V$ ,  $I_{D_Q} = 140$ mA, simulated results

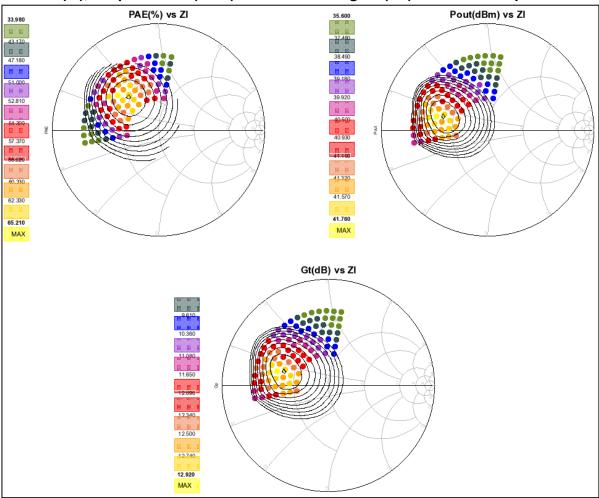

# **Elementary Cell Load Pull Performances**

Tref = +25°C,  $V_{DS} = +30V$ ,  $I_{D_Q} = 140$ mA, simulated results

The impedances are chosen as a trade-off between Output Power, PAE and Stability of the device. Second harmonic of output load has been tuned.

These values are given in the bonding pads reference plane.

| Frequency<br>(GHz) | Zs          | ZI          | Gain (dB)<br>@PAE <sub>max</sub> | Pout (W)<br>@PAE <sub>max</sub> | PAE <sub>max</sub><br>(%) | Pout <sub>max</sub><br>(W) |

|--------------------|-------------|-------------|----------------------------------|---------------------------------|---------------------------|----------------------------|

| 1                  | 11.6+ j28.4 | 51+ j20.3   | 16                               | 12.5                            | 75                        | 13.2                       |

| 3                  | 2.2+ j11    | 23.8+ j27.1 | 16                               | 11.4                            | 72                        | 12.4                       |

| 5                  | 1.3+ j5.5   | 11.4+ j20.7 | 15                               | 11.3                            | 69                        | 12.3                       |

| 7                  | 1.5+ j2.9   | 8.7+ j15.4  | 11.5                             | 11.2                            | 63                        | 12                         |

| 8                  | 1.3+ j1.6   | 5.4+ j13.4  | 10                               | 10.5                            | 62                        | 11                         |

UMS UMS

# Comparison Simulation/Measurement of Elementary Cell Load Pull Performances

Tref= +25°C, Vg pulsed mode 10µs - 10%, Freq=3GHz, V<sub>DS</sub>=28V, I<sub>D\_Q</sub>=0mA/mm (Class B)

- ZloadH2=ZloadH3=50Ω

- Zsource matched for maximum gain

- On wafer measurement

- Measurement are given in the transistor plan at 5dB of compression

PAE(%), Output Power (dBm) and transducer gain (dB) vs the load impedance

Measurements are represented by multicolour dots and model by black contours.

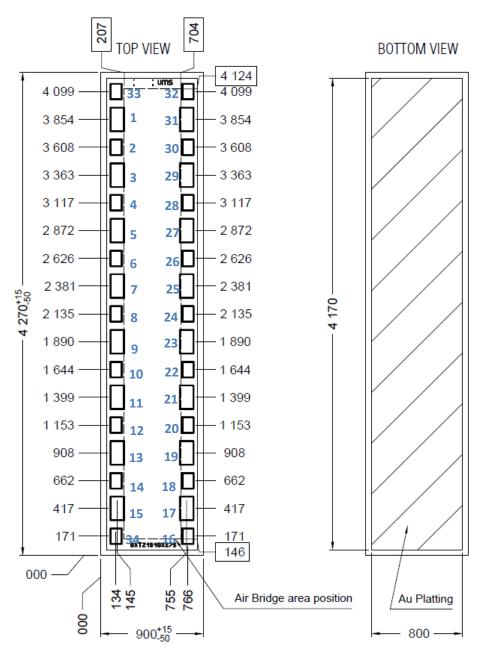

#### **Mechanical data**

Chip thickness: 100µm +/- 10 µm All dimensions are in micrometers

All Gate and Drain pads must be connected, ground connection is optional (source is grounded through vias hole)

| Reference     | Pad number                                       | Pad size     |

|---------------|--------------------------------------------------|--------------|

| DC Gate pads  | (1, 3, 5, 7, 9, 11, 13, 15)                      | 204 x 115µm² |

| DC Drain pads | (17, 19, 21, 23, 25, 27, 29, 31)                 | 204 x 115µm² |

| GND pads      | (2, 4, 6, 8, 10, 12, 14, 16, 18, 20, 22, 24, 26, | 117x113µm²   |

|               | 28, 30, 32, 33, 34)                              |              |

8/10

Ref.: DSCHK90130301 - 27 Oct 20

Spec

Specifications subject to change without notice

85W Power Transistor

CHK9013-99F

**Notes**

#### **Qualification domain**

This part is qualified according to UMS standards, excluding humid environment.

#### User guide for MMIC storage, pick & place, die attach, wire bonding

Refer to the application note AN0001 available at <a href="https://www.ums-rf.com">https://www.ums-rf.com</a> for general recommendations on chip handling.

#### Recommended environmental management

UMS products are compliant with the regulation in particular with the directives RoHS N°2011/65 and REACh N°1907/2006. More environmental data are available in the application note AN0019 also available at <a href="https://www.ums-rf.com">https://www.ums-rf.com</a>.

#### **Recommended ESD management**

Refer to the application note AN0020 available at <a href="https://www.ums-rf.com">https://www.ums-rf.com</a> for ESD sensitivity and handling recommendations for the UMS package products.

### **User guide GaN Power Bars Assembly guide lines**

Refer to the application note AN0026 available at <a href="https://www.ums-rf.com">https://www.ums-rf.com</a> for general recommendations on GaN-on-SiC Transistor handling and assembly.

# **Ordering Information**

Chip form: CHK9013-99F/00

Information furnished is believed to be accurate and reliable. However **United Monolithic Semiconductors S.A.S.** assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of **United Monolithic Semiconductors S.A.S.**. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. **United Monolithic Semiconductors S.A.S.** products are not authorised for use as critical components in life support devices or systems without express written approval from **United Monolithic Semiconductors S.A.S.**

Ref.: DSCHK90130301 - 27 Oct 20 10/10 Specifications subject to change without notice