# 9W 37-42GHz High Power Amplifier

#### **GaN Monolithic Microwave IC**

## **Description**

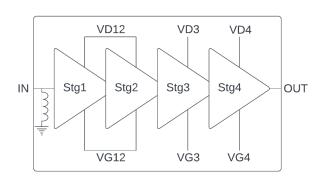

The CHA7453-99F is a four stages High Power Amplifier operating between 37 and 42GHz and providing typically 9W of saturated output power and 23% of Power Added Efficiency. The typical power supply is 20V/290mA (quiescent current). Thanks to a low drain voltage biasing, the CHA7453-99F provides a junction temperature below 160°C, even in saturation.

The circuit is manufactured on a space qualified GaN-on-SiC HEMT process and is available in bare die form.

It is firstly dedicated to space, military and telecom applications and well suited for a wide range of microwave applications and systems.

### **Main Features**

■ Frequency range: 37 – 42GHz

■ High output power: 9W■ High PAE: 23%

■ Linear Gain: above 24dB ■ DC bias: Vd=20V @Id=290mA

■ Chip size: 3.6x2.9mm²■ Available in bare die

| Main Electrical Characteristics                                               |                        |      |      |      |     |  |

|-------------------------------------------------------------------------------|------------------------|------|------|------|-----|--|

| T <sub>Backside</sub> = +25°C (T <sub>case</sub> : Chip backside temperature) |                        |      |      |      |     |  |

| Symbol                                                                        | Parameter Min Typ Max  |      |      |      |     |  |

| Freq                                                                          | Frequency range        | 37.5 |      | 41.5 | GHz |  |

| Gain                                                                          | Linear Gain            |      | 28   |      | dB  |  |

| Pout                                                                          | Saturated Output Power |      | 39.5 |      | dBm |  |

| PAE                                                                           | Power Added Efficiency |      | 23   |      | %   |  |

Ref.: DSCHA7453-99F-3354 - 21 Dec 23

## **Specifications**

### T<sub>Backside</sub> = +25°C, Vd = +20V, CW excitation

| Symbol | Parameter                    | Min  | Тур  | Max  | Unit |

|--------|------------------------------|------|------|------|------|

| Freq   | Frequency range              | 37.5 |      | 41.5 | GHz  |

| Gain   | Linear Gain                  |      | 28   |      | dB   |

| Pout   | Saturated Output Power       |      | 39.5 |      | dBm  |

| PAE    | Power Added Efficiency       |      | 22   |      | %    |

| ld     | Drain current at saturation  |      | 2.5  |      | Α    |

| S11    | Input Return Loss            |      | -12  |      | dB   |

| S22    | Output Return Loss           |      | -8   |      | dB   |

| ldq    | Quiescent Drain bias current |      | 290  |      | mA   |

| Vd     | Drain voltage                |      | 20   |      | V    |

These values are representative of on-board measurements as defined on the drawing in paragraph "Recommended assembly plan".

## Absolute Maximum Ratings (1)

T<sub>Backside</sub> = +25°C

| Symbol | Parameter                    | Values   | Unit |

|--------|------------------------------|----------|------|

| Vd     | Drain bias voltage           | 27       | V    |

| ld     | Quiescent Drain bias current | 800      | mA   |

| Vg     | Gate bias voltage            | -7 to -1 | V    |

| Pin    | Maximum Input Power          | 22       | dBm  |

<sup>(1)</sup> Operation of this device above anyone of these parameters may cause permanent damage.

## Recommended Operating Range (2), (3)

| Symbol | Parameter                        | Values     | Unit |

|--------|----------------------------------|------------|------|

| Vd     | Drain bias voltage               | 18 to 25   | V    |

| ld     | Drain bias current               | 100 to 450 | mA   |

| Vg     | Gate bias voltage                | -5 to -2.5 | V    |

| Tj     | Maximum Junction temperature (4) | 200        | °C   |

<sup>(2)</sup> Electrical performances are defined for specified test conditions

## **Temperature Range**

| T <sub>Backside</sub> | Operating temperature range at MMIC backside level | -40 to +95  | °C |

|-----------------------|----------------------------------------------------|-------------|----|

| T <sub>stg</sub>      | Storage temperature range                          | -55 to +150 | °C |

<sup>(3)</sup> Electrical performances are not guaranteed over all recommended operating conditions

<sup>(4)</sup> See Device thermal performances section

### **Typical Bias Conditions**

#### T<sub>Backside</sub>=+25°C

| Symbol | Pad N°                   | Parameter                        | Values | Unit |

|--------|--------------------------|----------------------------------|--------|------|

| Vg     | 3, 5, 7,<br>25, 27, 29   | Gate voltage tuned for Idq~290mA | -3.1   | V    |

| Vd     | 9, 11, 13,<br>19, 21, 23 | Drain Voltage                    | 20     | V    |

# "Power ON" sequence

- 1. Bias HPA gate voltage at Vg close to Vpinch-off (Vg~-5V)

- 2. Set Vd bias voltage to 0V: Id=0mA

- 3. Apply Vd bias voltage, Vd = 20V: Id=0mA

- 4. Set Vc bias voltage to 5V for Detector biasing

- 5. Increase Vg up to quiescent bias drain current Idq=216mA

- 6. Apply RF input Power

# "Power OFF" sequence

- 1. Turn off RF input power

- 2. Bias HPA Gate voltage at Vg~-5V: Id=0mA

- 3. Decrease Vd bias voltage down to 0V

- 4. Set Vc bias voltage to 0V

- 5. Turn Vg bias voltage to 0V

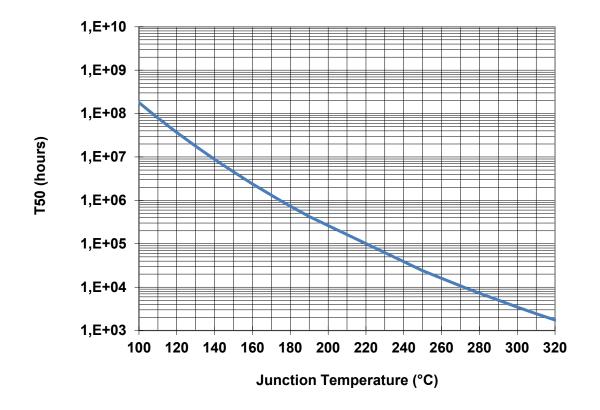

### **Device thermal performances**

All the figures given in this section are obtained assuming that the device is only cooled down by conduction through the thermal pad (no convection mode considered).

The temperature is monitored at the chip back-side interface (Tcase).

For nominal operating, the system maximum temperature must be adjusted in order to guarantee that the Junction Temperature remains below the maximum value specified in the Recommended Operating Ratings table.

Therefore, the system PCB must be designed to comply with this requirement.

| Thermal<br>Resistance (1) | R <sub>th_eq</sub> | $T_{\text{Backside}} = 85^{\circ}\text{C},$                            | 2.36  | °C/W |

|---------------------------|--------------------|------------------------------------------------------------------------|-------|------|

| Junction<br>Temperature   | Tj                 | Vd = 20V, Idq = 290 mA,<br>Pin = 18 dBm, Freq = 41GHz,<br>Pdiss = 28 W | 151   | °C   |

| Median Life               | T50                | Paiss = 28 VV                                                          | 3.5E6 | Hrs  |

<sup>&</sup>lt;sup>1</sup> Thermal resistance measured at the backside of the chip

Measurements reference plane is de-embedded at the wire-bondings planes of the RF lines.

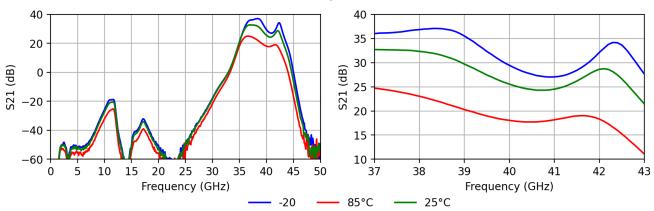

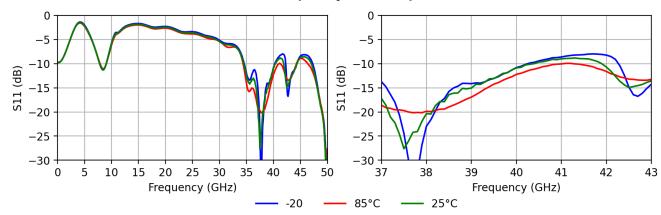

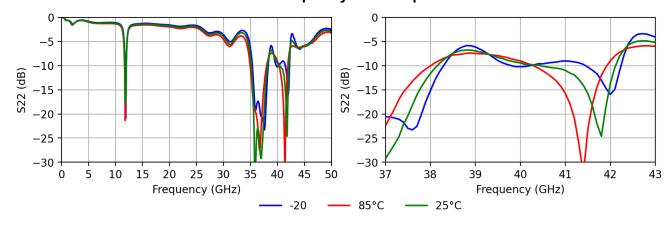

### Performance versus frequency and temperature

Test conditions :  $V_D$  = 20V,  $I_{dq}$  = 290mA,  $T_{Backside}$  = -20°C / 25°C / 85°C

### **S21 versus Frequency and Temperature**

#### **S11 versus Frequency and Temperature**

#### **S22 versus Frequency and Temperature**

Measurements reference plane is de-embedded at the wire-bondings planes of the RF lines.

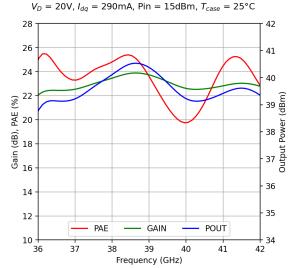

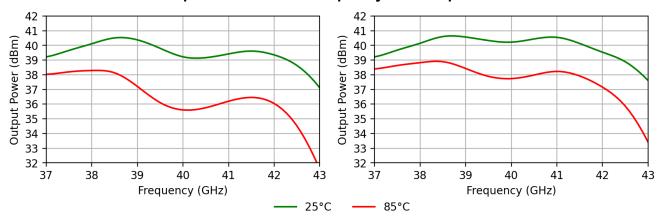

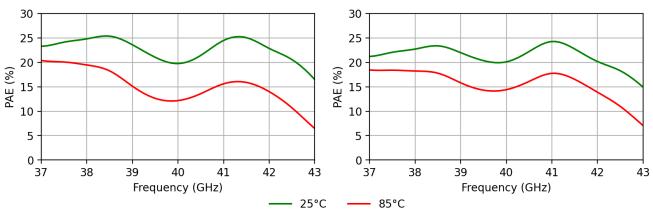

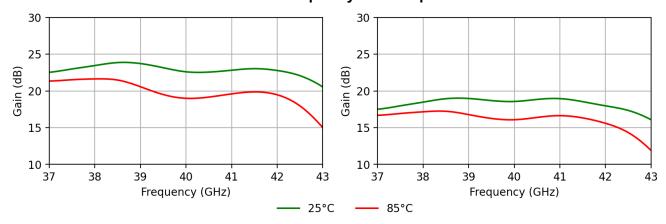

#### Performance versus frequency and temperature

Test conditions :  $V_D = 20V$ ,  $I_{dq} = 290mA$ ,  $T_{Backside} = 25^{\circ}C / 85^{\circ}C$

### **Output Power versus Frequency and Temperature**

### **Power Added Efficiency versus Frequency and Temperature**

#### **Gain versus Frequency and Temperature**

Ref.: DSCHA7453-99F-3354 - 21 Dec 23

Measurements reference plane is de-embedded at the wire-bondings planes of the RF lines.

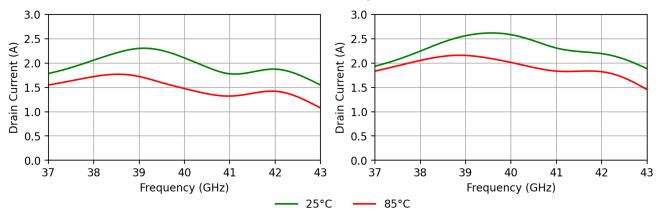

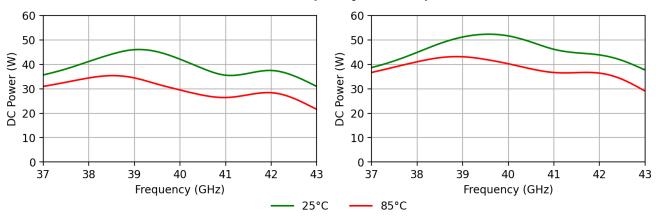

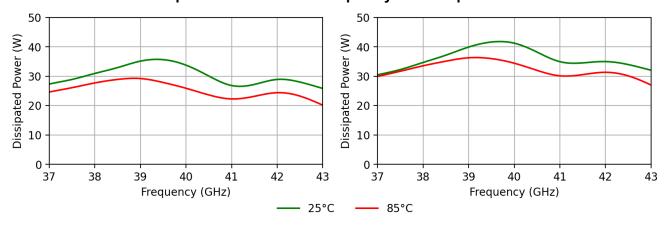

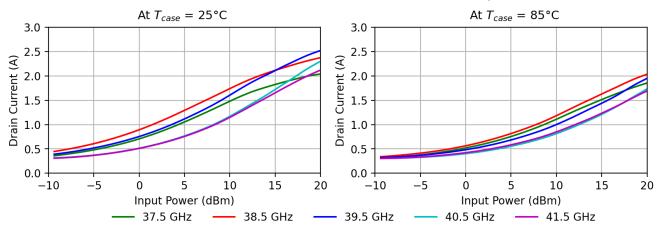

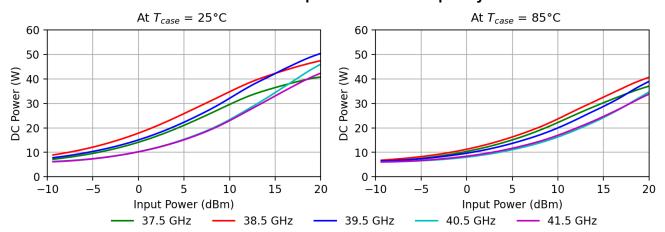

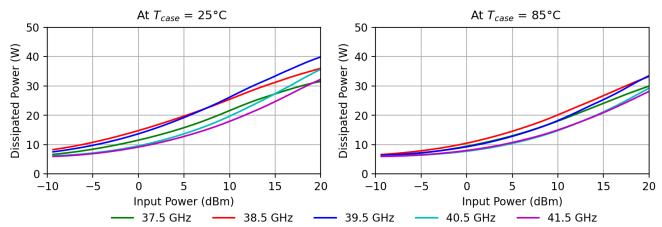

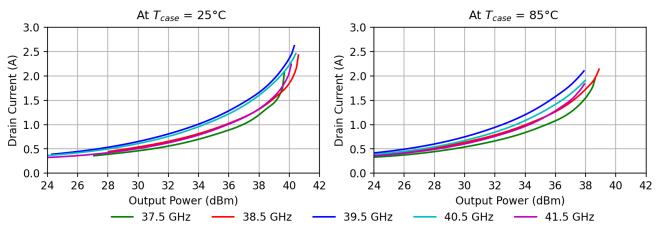

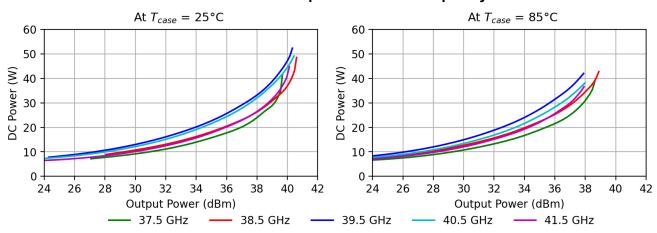

#### Performance versus frequency and temperature

Test conditions :  $V_D$  = 20V,  $I_{dq}$  = 290mA,  $T_{Backside}$  = 25°C / 85°C

### **Drain Current versus Frequency and Temperature**

#### **DC Power versus Frequency and Temperature**

#### **Dissipated Power versus Frequency and Temperature**

Ref.: DSCHA7453-99F-3354 - 21 Dec 23

Measurements reference plane is de-embedded at the wire-bondings planes of the RF lines.

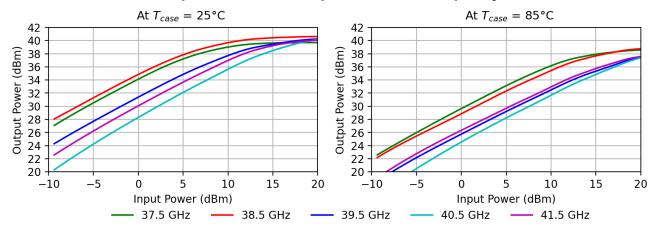

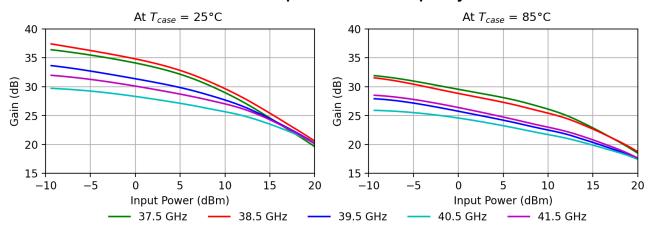

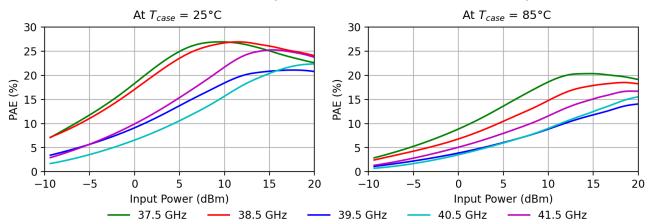

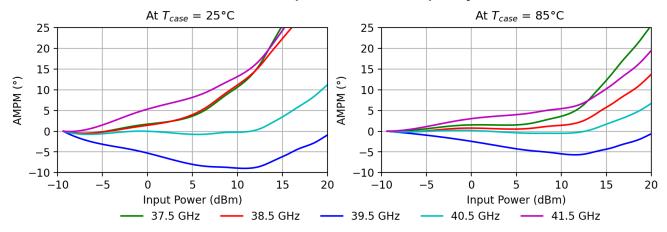

### **Performance versus Input Power and Frequency**

Test conditions :  $V_D = 20V$ ,  $I_{dq} = 290mA$ ,  $T_{Backside} = 25^{\circ}C / 85^{\circ}C$

### **Output Power versus Input Power and Frequency**

#### **Gain versus Input Power and Frequency**

#### Power Added Efficiency versus Input and versus Frequency

Ref.: DSCHA7453-99F-3354 - 21 Dec 23

Measurements reference plane is de-embedded at the wire-bondings planes of the RF lines.

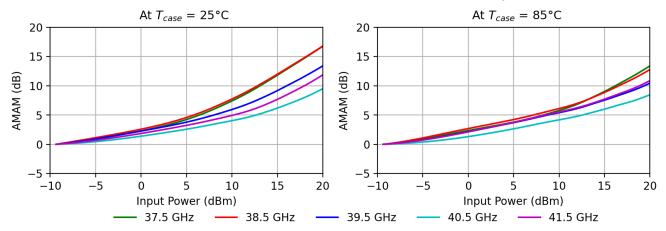

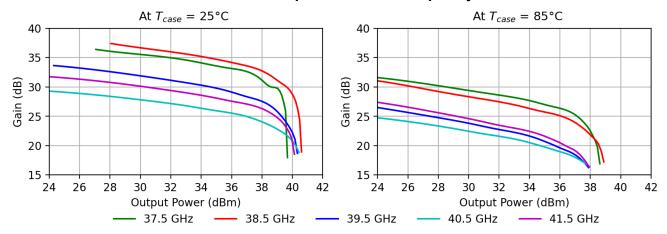

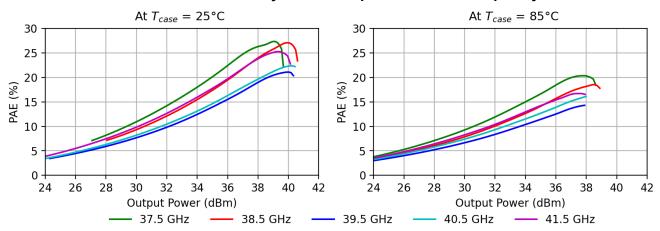

#### **Performance versus Output Power and Frequency**

**Test conditions**:  $V_D = 20V$ ,  $I_{dq} = 290mA$ ,  $T_{Backside} = 25^{\circ}C / 85^{\circ}C$

### **AMAM distortion versus Input Power and Frequency**

#### **AMPM versus Input Power and Frequency**

#### **Drain Current versus Input Power and Frequency**

Measurements reference plane is de-embedded at the wire-bondings planes of the RF lines.

#### **Performance versus Input Power and Frequency**

Test conditions :  $V_D = 20V$ ,  $I_{dq} = 290mA$ ,  $T_{Backside} = 25^{\circ}C / 85^{\circ}C$

#### **DC Power versus Input Power and Frequency**

### **Dissipated Power versus Input Power and Frequency**

Measurements reference plane is de-embedded at the wire-bondings planes of the RF lines.

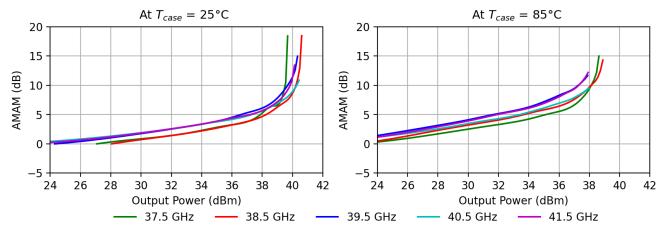

#### **Performance versus Output Power and Frequency**

Test conditions :  $V_D$  = 20V,  $I_{dq}$  = 290mA,  $T_{Backside}$  = 25°C / 85°C

#### **Gain versus Output Power and Frequency**

#### **Power Added Efficiency versus Output Power and Frequency**

### **AMAM distortion versus Output Power and Frequency**

Ref.: DSCHA7453-99F-3354 - 21 Dec 23

Measurements reference plane is de-embedded at the wire-bondings planes of the RF lines.

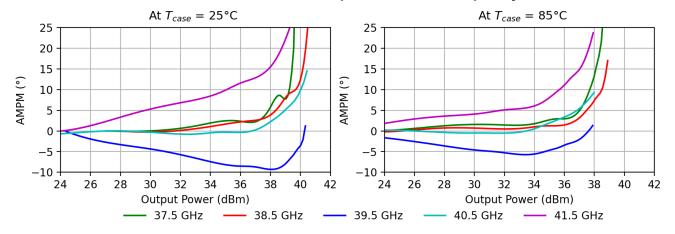

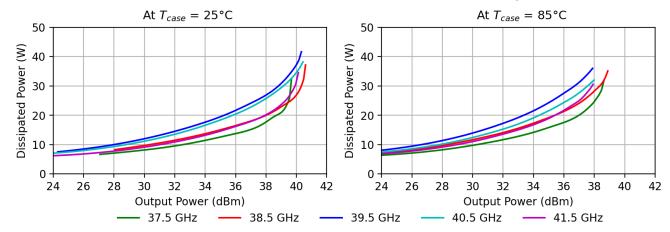

### **Performance versus Output Power and Frequency**

**Test conditions**:  $V_D = 20V$ ,  $I_{dq} = 290mA$ ,  $T_{Backside} = 25^{\circ}C / 85^{\circ}C$

### **AMPM distortion versus Output Power and Frequency**

#### **Drain Current versus Output Power and Frequency**

#### **DC Power versus Output Power and Frequency**

Ref.: DSCHA7453-99F-3354 - 21 Dec 23

Measurements reference plane is de-embedded at the wire-bondings planes of the RF lines.

### **Performance versus Output Power and Frequency**

Test conditions :  $V_D$  = 20V,  $I_{dq}$  = 290mA,  $T_{Backside}$  = 25°C / 85°C

## **Dissipated Power versus Output Power and Frequency**

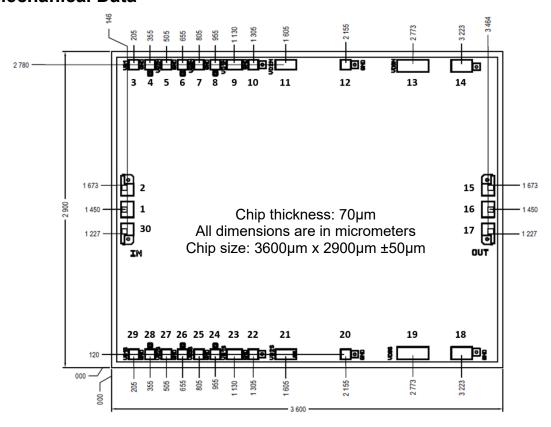

### **Mechanical Data**

| PAD Number                                          | Name   | Description                                                      | Pad size       |

|-----------------------------------------------------|--------|------------------------------------------------------------------|----------------|

| 1                                                   | RF IN  | Input RF port                                                    | 186µm x 105µm  |

| 3                                                   | G12    | DC Gait voltage, 1st & 2st stage, North                          | 96µm x 96µm    |

| 5                                                   | G3     | DC Gate voltage 3 <sup>d</sup> stage, North                      | 96µm x 96µm    |

| 7                                                   | G4     | DC Gate voltage 4 <sup>th</sup> stage, North                     | 96µm x 96µm    |

| 9                                                   | D12    | DC Drain voltage, 1 <sup>st</sup> & 2 <sup>st</sup> stage, North | 146µm x 96µm   |

| 11                                                  | D3     | DC Drain voltage 3 <sup>d</sup> stage, North                     | 196µm x 96µm   |

| 13                                                  | D4     | DC Drain voltage 4 <sup>th</sup> stage, North                    | 296µm x 116µm  |

| 16                                                  | RF OUT | Output RF port                                                   | 118 µm x146 µm |

| 19                                                  | D4     | DC Drain voltage 4 <sup>th</sup> stage, South                    | 296µm x 116µm  |

| 21                                                  | D3     | DC Drain voltage 3 <sup>d</sup> stage, South                     | 196µm x 96µm   |

| 23                                                  | D12    | DC Drain voltage, 1st & 2st stage, South                         | 146µm x 96µm   |

| 25                                                  | G4     | DC Gate voltage 4 <sup>th</sup> stage, South                     | 96µm x 96µm    |

| 27                                                  | G3     | DC Gate voltage 3 <sup>d</sup> stage, South                      | 96µm x 96µm    |

| 29                                                  | G12    | DC Gait voltage, 1 <sup>st</sup> & 2 <sup>st</sup> stage, South  | 96µm x 96µm    |

| 2,4,6,8,10,12,14<br>,15,17,18,20,22,<br>24,26,28,30 | GND    | Ground                                                           | 96µm х 96µm    |

UMS

## **Recommended Assembly Plan**

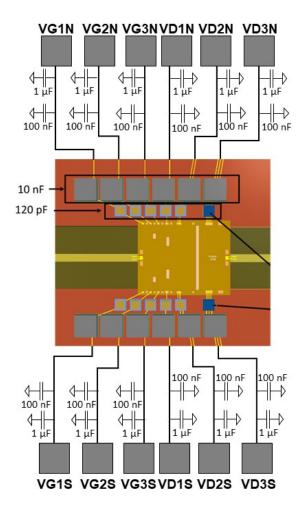

4 levels of decoupling capacitor have been used, 2 on the tab and 2 on the board. The first level is composed of 120 pF chip capacitors, the second level is composed of 10nF chip capacitors, the third level is composed of 100nF SMD 1210 capacitors and the fourth stage is composed of 1 $\mu$ F SMD 1206 capacitors. The first two levels should be as close as possible to the die.

## **ESD Sensitivity**

| Parameter              | Classification | Standard                 |

|------------------------|----------------|--------------------------|

| Human Body Model (HBM) | 1A             | ANSI/ESDA/JEDEC - JS-001 |

## CHA7453-99F

## 9W 37-42GHz Power Amplifier

### Recommended reflow process assembly

Refer to the application note AN0001 available at https://www.ums-rf.com for die attach.

### Recommended environmental management

UMS products are compliant with the regulation in particular with the directives RoHS N°2011/65 and REACh N°1907/2006. More environmental data are available in the application note AN0019 also available at https://www.ums-rf.com.

### Recommended ESD management

Refer to the application note AN0020 available at https://www.ums-rf.com for ESD sensitivity and handling recommendations for the UMS products.

## **Ordering Information**

Ref.: DSCHA7453-99F-3354 - 21 Dec 23

CHA7453-99F/00 Chip form:

Information furnished is believed to be accurate and reliable. However United Monolithic Semiconductors S.A.S. assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of United Monolithic Semiconductors S.A.S.. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. United Monolithic Semiconductors S.A.S. products are not authorised for use as critical components in life support devices or systems without express written approval from United Monolithic Semiconductors S.A.S.

16/16

Bât. Charmille - Parc Mosaic - 10, Avenue du Québec - 91140 VILLEBON-SUR-YVETTE - France Tel.: +33 (0) 1 69 86 32 00 - Fax: +33 (0) 1 69 86 34 34 - www.ums-rf.com